第2章

.......

entity MDPGen is

vBlnk

ZROW.

IEEE.std\_logic\_thr ColDecode

IEEE.std\_logic\_arith.allf:i

## FPGA活用回路& HDLサンプル記述13連発!

川岡圭一,河野崇,相田泰志,田中良平,松石剛啓,吉田政和

FPGAを活用した13種類のサンプル回路を紹介する。ここで紹介するのは、FPGAを使ったボード・レベルの回路図と、FPGAの内部を記述したHDLソース・コードである。所望の信号を入出力するためには、多くの場合、FPGAの外部にいくつかの部品を組み合わせて構成した回路が必要になる。それを制御するのは当然FPGAであり、その機能はHDLで記述することになる。実際の設計や学習の参考回路として、本サンプル回路をおおいに役立ててほしい。(編集部)

本稿で紹介するサンプル回路を下掲の表にまとめました. 大きく分類すると,「ディジタル入力回路関連」が3件,「ディジタル出力回路関連」が3件,「アナログ入力回路関連」が1件,「アナログ出力回路関連」が3件,「インターフェース回路関連」が3件になっています.

すべてのサンプル回路について,FPGAとその外付け部品で構成する回路図,およびFPGAに実装する機能ブロックのHDL記述を紹介しています.ただし,回路図において,FPGAの動作に共通して必要となる電源回路やコンフ

ィグレーション回路,クロックなどは省略しています.また,単独で動作する完全な回路図にはなっていません.図には,FPGAのI/Oを介して外部と接続するポートと,FPGAの内部でほかの機能ブロックとつなぐポートを示してあります.HDL記述についてはできるだけ誌面に示しています.ただし,ソース・コードが長くなってしまうものについては,本誌のホームページ(http://www.cqpub.co.jp/dwm/)からダウンロードできるようにしました.

ここで紹介する回路は、記事中で示した環境で実際に動作しているものです。ただし、評価のための簡易的な機能しか持たないものもあれば、実際の設計で活用した機能ブロックをそのまま紹介しているものもあります。回路の設計趣旨が記事ごとに異なることをあらかじめご了承ください。

表 本稿で紹介するサンプル 回路

|       | 回路名                             | 分 類      | 主要部品          | ページ  |

|-------|---------------------------------|----------|---------------|------|

| No.1  | スイッチ入力回路                        | ディジタル入力  | 機械式スイッチ       | P.29 |

| No.2  | 4 × 4 マトリックス・スイッチ入力回路           | ディジタル入力  | 機械式スイッチ       | P.32 |

| No.3  | 外部機器からのディジタル入力回路                | ディジタル入力  | フォトカプラ        | P.34 |

| No.4  | 外部機器へのディジタル出力回路                 | ディジタル出力  | リレー , フォトカプラ  | P.36 |

| No.5  | 7 セグメント LED のダイナミック点灯回路         | ディジタル出力  | 7セグメント LED    | P.38 |

| No.6  | 2色ドット・マトリックス LED 点灯回路           | ディジタル出力  | ドット・マトリックスLED | P.41 |

| No.7  | アナログ入力回路                        | アナログ入力   | A-D コンバータ     | P.45 |

| No.8  | アナログ出力回路                        | アナログ出力   | 抵抗,コンデンサ      | P.48 |

| No.9  | 高速アナログ出力回路                      | アナログ出力   | D-A コンバータ     | P.50 |

| No.10 | 4 チャネル・アナログ出力回路                 | アナログ出力   | D-A コンバータ     | P.52 |

| No.11 | 同期 SR A M インターフェース回路            | インターフェース | ZBT-SSRAM     | P.54 |

| No.12 | PC カード・インターフェース回路               | インターフェース | CPLD          | P.56 |

| No.13 | I <sup>2</sup> C-bus インターフェース回路 | インターフェース | 抵抗,FET        | P.60 |

01

generic

## スイッチ入力回路

松石剛啓

外部回路

● 回路図:図1-1

●主要部品:機械式スイッチ(タクタイル・スイッチなど)

HDL 記述

● VHDL記述:リスト1-1 ● 外部入力: sw pulse in

●外部出力:なし

●内部入力: clk, rstn

● 内部出力: sw\_pulse\_out

● パラメータ: cha\_cnt\_max

(チャタリング除去用カウンタの最大値)

評価環境

ISE WebPACK 7.1i, Spartan- E

多くの機器では,入力デバイスとしてスイッチが用いられています(写真1-1).スイッチの状態や変化によって, LSIの動作を切り替えるという使いかたが一般的です.

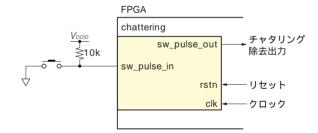

FPGA にスイッチを接続するもっとも簡単な回路を図1-1に示します.スイッチがOFF(接点が開いている)のときには,FPGA には"H"が入力されています.スイッチをONにすると,FPGA には"L"が入力されます.

" H "が" L "が入力されるだけなので, HDL記述は簡単そうです. しかし,機械式のスイッチを使うときには注意し

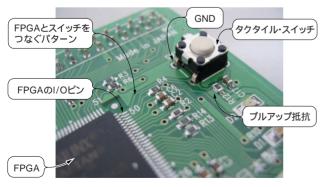

写真1-1 FPGA に接続されたスイッチ

プリント基板に実装された FPGA とスイッチ . FPGA の I/O ピンにスイッチ が接続されていることがわかる .

なければならないことがあります.

## ● 機械式スイッチではチャタリングが発生

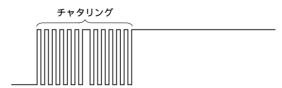

機械式のスイッチやリレーは,接点が切り替わるとき,接点部のバウンドにより短い時間にON/OFFを繰り返すチャタリング(バウンシングともいう)という現象が発生します(図1-2).このチャタリングを考慮せずに回路を設計すると,誤動作してしまうことがあります.

例えば,スイッチをON した回数を数えたいとき,チャタリングが発生すると,1回のONでも数回と認識してしまいます.

チャタリングの時間は,スイッチやリレーの種類によって異なります.一般的なスイッチでは数msのものが多いようです.これはデータシートに明示されているので,使用する部品の特性を確認して設計しなければなりません.

## ● カウンタを使ってチャタリングを除去

チャタリングの影響を除去するためには,いくつかの方法があります.ここでは,一定時間ON/OFFが続いたときのみON/OFFと判断する方法を考えます.

図1-1 FPGA にスイッチを接続するもっとも簡単な回路

スイッチがOFFのときには , FPGAには" H "が入力されている . スイッチをONにすると , FPGAには" L "が入力される .

図1-2 チャタリングの波形

機械式のスイッチやリレーは,接点が切り替わるとき,接点部のバウンドによって短い時間にON/OFFを繰り返す.